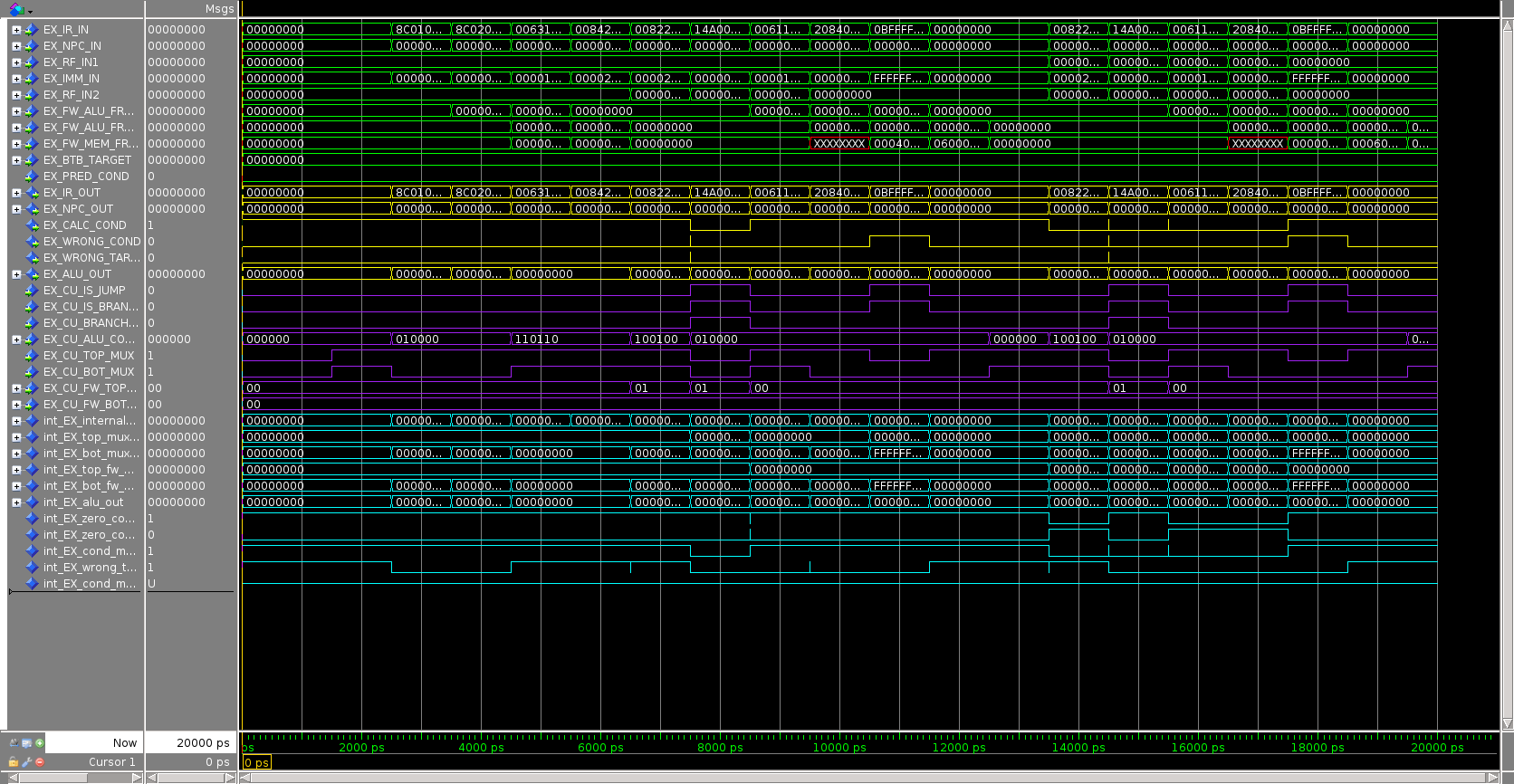

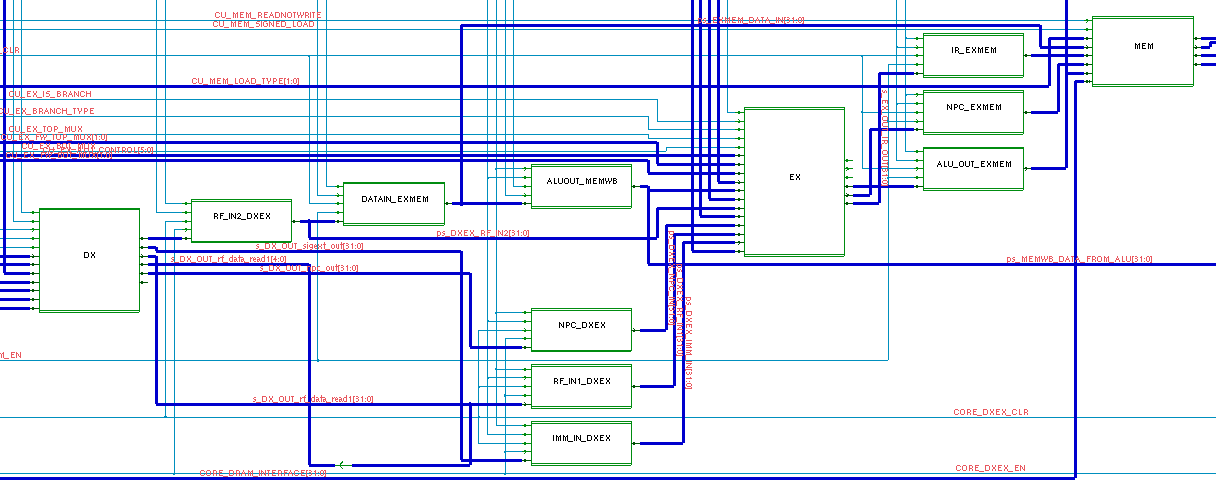

This project is mainly focused on design, simulation and synthesis of a 32-bit DLX microprocessor with Branch Prediction Unit and Forwarding Logic. The device has been proved to successfully work with the MIPS32 Instruction Set Architecture (Integer Operations only). The microprocessor has been design on a low level RTL using VHDL and simulated and tested with ModelSim (by Mentor Graphics). This is an example the dump of all signals of the Execution Stage during the simulation of a software multiplication (emulation using shifts and additions only).

Afterwards it has been synthesized with DC Compiler (by Synopsys) targeting two different technology processes: 65 nm using STMicroelectronics libraries, 45 nm using NanGate libraries. (Click on the image to enlarge)

With STMicroelectronics library, we targeted high performance both in timing and in power. Regarding power consumption, the developed script works both on leakage power and on dynamic power using Dual-Vth assignment and clock gating.

The maximum operating frequency is about 700 MHz and furthermore, both the techniques used to reduce power work as expected. On one hand, about 45% of total cells have been swapped to an high threshold voltage: this means that without modifying the timing constrains, we achieve more than 90% of leakage reduction. On the other hand, clock gating reduces the total dynamic power of about 25%, applying automatically this technique to the 67% of total registers in the design.

Finally, the processor has been physically compiled and mapped using Encounter (by Cadence).